目前,手机处理器是7nm,台积电即将量产5nm芯片,未来还有3nm、2nm,甚至1nm。根据台积电研发负责人在谈论半导体工艺极限问题时,认为到了2050年,晶体管可以达到氢原子尺度,即0.1nm,那么半导体工艺的“物理极限”是什么呢?

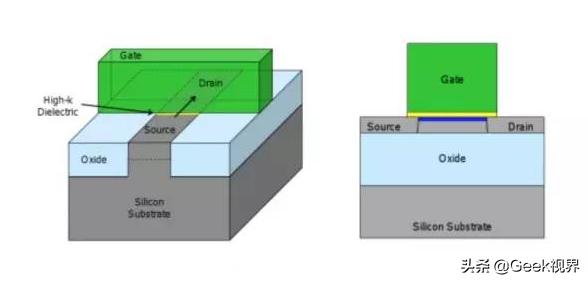

制程工艺首先,我们了解一下芯片的制程工艺。华为的麒麟990处理器,指甲壳大小,集成了上百亿的晶体管,单个晶体管的结构如下图所示▼。

在晶体管中,电流是从源极(Source)流向漏极(Drain),而栅极(Gate)相当于闸门,主要负责两端源极和漏极的通断。通代表1,断代表0,这样就实现了计算机世界的0、1运算。栅极的宽度,也称为删长,就是所说的xx nm制程工艺。

通常来说,制程工艺越小,晶体管删长越小,电流通过时的损耗越少,表现出来就是手机常见的发热和功耗。同时,单位面积的芯片可以容纳更多的晶体管。因此,晶圆代工厂不断的升级技术,力求将栅极宽度做的越来越窄。然而,工艺的提升会受到光刻机技术、芯片“物理极限”等多方面因素的限制。

如何突破技术限制?①更换材料。目前,芯片采用的是硅基半导体结构,根据台积电的规划,今年实现5nm工艺,2022年实现3nm工艺,2024年实现2nm工艺,正在逼近1nm。2017年,IBM科研团队在实验室环境下,使用碳纳米材料,制造出了1nm的晶体管,1nm工艺后的芯片,可能采用纳米片、碳纳米管等新材料。

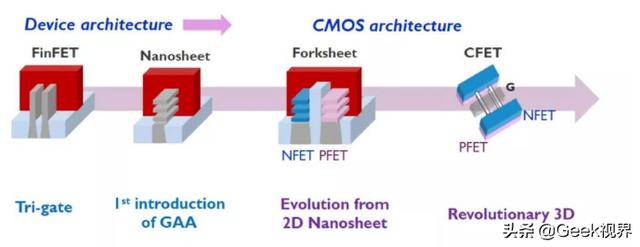

②结构的升级。目前,芯片制造采用了FinFET结构,随着工艺的提升,FinFET技术探底,新的结构将会诞生。2nm技术节点将会爱用Forsheet结构,1nm节点是采用CFET结构。

不过,芯片制造总是有“物理极限”的,将会产生“量子效应”,PN结不能形成之前的工作状态,无法表现出0和1这种状态,取代数字电路的技术可能就是“量子计算”了。

如果觉得对你有帮助,可以多多点赞哦,也可以随手点个关注哦,谢谢。